Check out our latest products

Working with MeitY to provide EDA tools to academia and startups, how does Cadence Design Systems benefit from this alliance? Discussing this, along with the company’s growth plans in India and its focus on AI-driven chip design, Cadence’s Jayashankar Narayanankutty speaks with EFY’s Yashasvini Razdan.

Q. With Cadence’s participation in the DLI scheme and Chip to Startup (C2S) programme, how does providing software at reduced rates impact you financially?

A. It may surprise you, but it has been very beneficial. The Design-Linked Incentive (DLI) Scheme lowers entry barriers. Earlier, if 10 companies were starting in this space, today that number has grown to 50. While we provide electronic design automation (EDA) tools to the government at a certain cost, the increased volume offsets any potential financial strain.

Startups receive the tools from the government at no cost, a major shift from earlier models. While we initially anticipated some financial impact from the DLI model, we were pleasantly surprised to see the opposite. Supporting this initiative has a long-term impact on the ecosystem, and we view it as an investment. The results speak for themselves—our business from startups has grown significantly in 2024, and we hope the trend continues into 2025.

Q. Could you explain the tailored business models Cadence has for startups and how they help address financial and technological challenges?

A. Our model is tailored to each startup’s unique needs, timelines, and funding stages. For example, some proofs-of-concept (POCs) may take six months, others 18 months or longer.

Startups typically begin with initial funding from family or Angel investors then progress to seed funding, followed by Series A, B, or C funding rounds. Depending on their stage, we structure commercial contracts to align with their cash flow. For instance, we might provide tools at a lower upfront cost and the remainder deferred until they secure further funding.

This approach reflects our trust in their success while addressing the high initial costs of semiconductor design. To put it in perspective, developing a good chip costs $25 to $30 million. Within this context, our flexible model significantly helps startups manage their financial challenges.

Q. What emerging trends in electronics chip design could encourage more startups to design in India?

A. The mid-end-range range of chip technologies offers immense opportunities. For instance, fabs at mature nodes remain highly valuable for volume-based applications. India imports a large number of electronics components and goods, representing opportunities for indigenisation in areas like consumer electronics and automotive components. While high-end chip design offers potential, the mid-end-range is the sweet spot for value creation and scaling. To support startups, we may offer tools at a lower upfront cost with the remainder deferred, making it easier for them to access essential design resources.

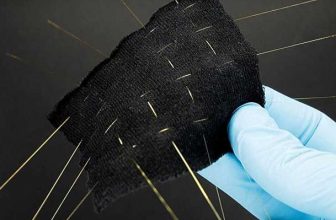

Q. You are focusing on three-dimensional (3D) integrated circuits (ICs). How do you see India adopting this technology?

A. If there is one technology where India can immediately take a leadership position, it is 3D ICs. This is because 3D ICs are a relatively new domain globally—no country has extensive tribal knowledge or established expertise. If India invests wisely, it could leapfrog and become a leader in this area. 3D ICs are the future, as they allow dies manufactured at different nodes (like 2 nanometres and 28 nanometres) to be integrated into a single package. While this reduces costs and enhances performance, it also introduces challenges such as functional verification and routing complexities.

Since these challenges are global, India can position itself at the forefront of 3D IC development by addressing them. I believe 3D ICs could be India’s best chance to take lead in the semiconductor industry.

Q. How is Cadence leveraging AI in chip design, and what opportunities does this create for Indian designers?

A. Cadence invested early in creating a big data platform called JedAI (Joint Enterprise Database and Artificial Intelligence). This platform allows our tools to handle vast amounts of data and extract actionable insights. The fundamental purpose of AI, in my view, is to accelerate the human in the loop. Until we reach a point of singularity, AI enhances human productivity by reducing the learning curve and enabling engineers to explore thousands of design possibilities in less time. This means less trial-and-error and more innovation.

Q. Could you list any AI-powered tools Cadence offers for design engineers?

A. A partial list of of our AI-powered tools include:

- Cerebrus: A back-end physical design tool for optimisation

- Virtuoso Studio: Custom and analog IC design generative AI application with support for systems, including RF, mixed-signal, photonics, and advanced heterogeneous designs

- Verisium: A functional verification tool that accelerates debugging

- Alegro X: A tool for printed circuit board (PCB) design

Q. Are AI-enabled tools accessible to startups and accelerators?

A. Yes, such tools are accessible to startups, but AI enablement might not be a priority for them initially. At the POC stage, where startups are investing heavily in developing and validating their ideas, it takes time to teach a machine to address problems that have not yet been fully explored. AI makes more sense during the production stage, where optimisations and efficiency gains have a greater impact.

While AI is often marketed as a game-changer, its practicality depends on the specific stage and needs of a startup. At the early stages, mastering the basics and focusing on core development is more critical.

Q. Is AI the only way to reduce time-to-commercialisation for chip designers?

A. AI is a powerful tool to reduce time to market, along with other approaches. There are other strategies as well, such as reusing proven designs in 3D ICs. Startups can also benefit from using pre-designed and silicon-proven intellectual property (IP) blocks. Cadence provides these blocks along with subsystems, which most other major IP vendors do not offer. System-level integration and innovation at the board and software levels can also contribute to faster market readiness.

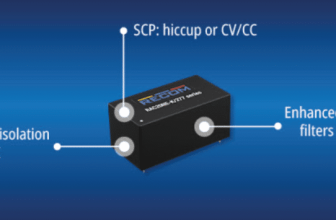

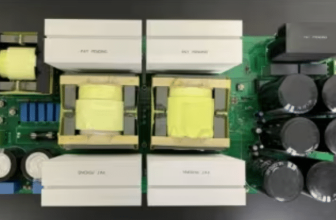

Cadence also has tools such as Palladium and Protium that allow hardware-software co-development. Palladium is a data-centre-sized rack for chip verification, emulating the chip before silicon is fabricated. Protium is a desktop-sized emulator that allows software engineers to write and test code as though they were working directly on the chip. When the silicon returns from fabrication, the software is already developed and ready.

Combined with AI, these strategies create a comprehensive approach to bringing products to market efficiently.

Q. How does Cadence plan to stay ahead in an AI-driven chip design environment?

A. Our strategy includes:

- Long-term investments: Platforms like JedAI and targeted hardware (like, as I said, Palladium and Protium)

- Diversification: Expanding into complementary domains like computational fluid dynamics and life sciences

- Pervasive AI integration: Embedding intelligence at every level of our tools

- Targeted hardware: Developing systems optimised for specific applications

Q. You are working with AICTE and academic institutes to develop a VLSI curriculum. What skills are you prioritising in this initiative?

A. The VLSI (very large-scale integration) curriculum is structured into three levels—basic electronics, device physics, and design processes. Our primary focus is on design—the third level.

We developed a curriculum with the All India Council for Technical Education (AICTE) and released it last year. This involved training 100 professors in teaching VLSI concepts, conducting sessions, and familiarising students with the subject. We even brought in an instructor from Israel to train them. Our efforts aim to instil design capabilities in engineers, in addition to implementation capabilities, defining products, working with specifications, and traversing the distance from concept to product.

Q. Why do knowledge gaps among fresh VLSI graduates in India exist?

A. Continuous advancements in the semiconductor industry require designers to adapt continuously to account for double patterning, gates all around, and extreme ultraviolet lithography, among others. The main challenge is the obsolescence of knowledge, which often outpaces universities. While some improvements have happened over three decades, especially in implementation, the problem-solving mindset still needs attention. Students excel in predefined problems but struggle with defining problems themselves. The industry increasingly demands such capabilities, and bridging this gap remains a key focus.

Q. How can students and researchers stay updated with constantly changing technology?

A. At our end, we operate on three levels — tools, learning material and competency development. We provide academic institutions with the same commercial tools engineers use globally, ensuring students work in real-world design environments. Professors and doctoral students receive extensive resources, enabling them to teach practical problem-solving. Digital Badges certify students and professionals in specific design areas, adding value to their resumes.

![[5G & 2.4G] Indoor/Outdoor Security Camera for Home, Baby/Elder/Dog/Pet Camera with Phone App, Wi-Fi Camera w/Spotlight, Color Night Vision, 2-Way Audio, 24/7, SD/Cloud Storage, Work w/Alexa, 2Pack](https://m.media-amazon.com/images/I/71gzKbvCrrL._AC_SL1500_.jpg)

![[3 Pack] Sport Bands Compatible with Fitbit Charge 5 Bands Women Men, Adjustable Soft Silicone Charge 5 Wristband Strap for Fitbit Charge 5, Large](https://m.media-amazon.com/images/I/61Tqj4Sz2rL._AC_SL1500_.jpg)